| Mon., 2/4    | Quiz Ch 4 & 5, Lab 4: Transformers, Diodes, & Power Supplies | HW4: (download) & Ch4 pr 1,2,5; Ch5 pr 3,12 |

|--------------|--------------------------------------------------------------|---------------------------------------------|

| Tues.,2/5    | Ch 8.19: Transistors                                         |                                             |

| Thurs., 2/7  | Discussion of Ch 8                                           | Lab 4 Notebook                              |

| Mon., 2/11   | Quiz Ch 8, Lab 5: Transistors                                | HW5: (download)                             |

| Tues.,2/12   |                                                              |                                             |

| Thurs., 2/14 | Midterm Review                                               | Lab 5 Notebook                              |

Handout (in lecture):

- biasing example

- FET diagram (corrected from Holton)?

Study List for Quiz #5: The quiz will be on Monday, October 20.

- 1. Rules for the NPN bipolar junction transistors.

- 2. Simple transistor devices.

# **Equation List**:

$$I_B = I_E - I_C \qquad \qquad I_C = \boldsymbol{b}I_B$$

Bipolar Junction Transistor - concentrate on NPN type

- Use H&H model of transistor as valve a current controls a current

- Basic rules

- Darlington Configuration boosts current amplification

- Example devices:

- Current Source

- ♦ Transistor Switch

- Emitter Follower

- Common-Emitter Amplifier just a <u>little</u> about biasing

Field Effect Transistors (FET)

• A voltage controls a current

# Ch 8 Transistors

## 8.1 Intro

A diode is generally used in a not-so-subtle way; it's on or it's off; it's like an open switch and virtually no current flows, or it's like a closed switch and all the current you want flows.

A common transistor is essentially two of these devices back to back. As we'll see, this configuration allows for much subtler uses. Primarily amplifying – a small change in current at one terminal can result in a large change at another. The transistor is one of the essential components of Integrated Circuits. Integrated Circuits can be designed to do a

$V_E = V_B - 0.6 \text{ V}$ See handwritten notes. Try to frame all analysis as applications of these three relations.

wide range of things, from simply amplifying a signal to converting 2-chanel stereo into Doubly 5.1.

# 8.2 The Bipolar Junction Transistor

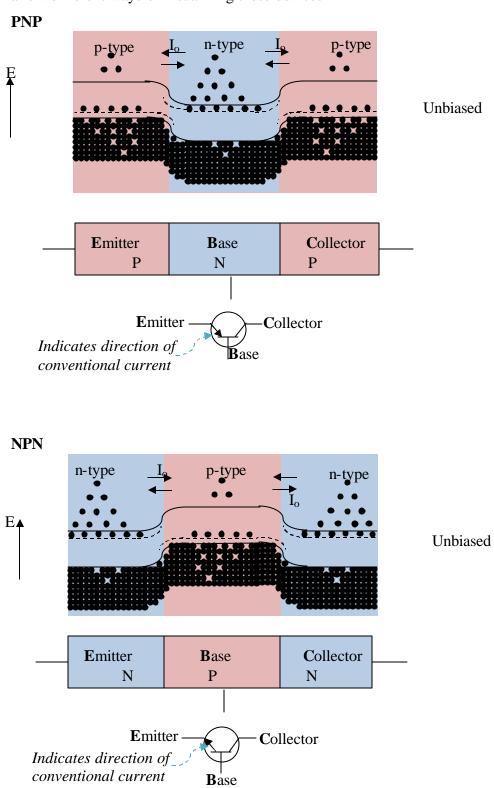

As a diode has two different ends – one that's P-doped (has more positively charged mobile holes than electrons) and one that's N-doped (has more negatively charged mobile electrons than holes), there are two simple kinds of transistors: P-N-P, and N-P-N. Here a few different ways of visualizing these devices

2

# 8.2.1 Transistor Operation

Just like a resistor with no voltage applied across it, the unbiased transistor doesn't do anything terribly interesting. So let's consider one of these things in action.

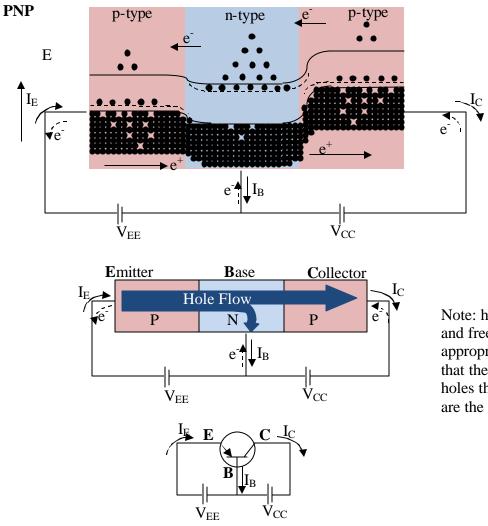

Note: had I drawn the free hole and free electron populations appropriately, it would be obviou that there are far more mobile holes than electrons, so the holes are the majority carriers.

Notice that the arrow within the transistor symbol points in the direction of the conventional current, and that the majority carriers (holes in this case) flow from the emitter toward the collector.

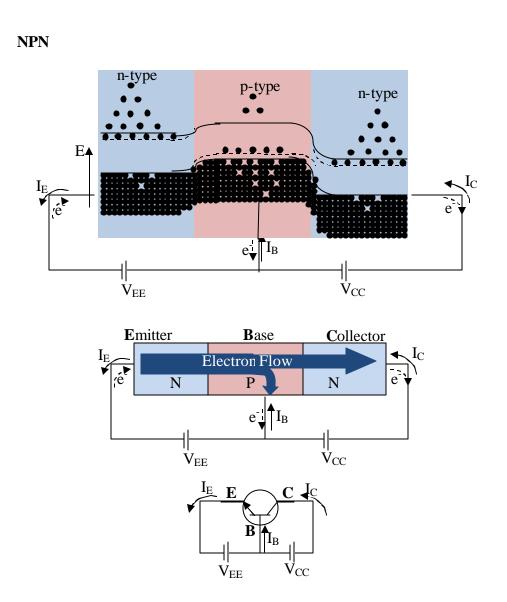

Again, notice that the arrow within the transistor symbol points in the direction of the conventional current, and that the majority carriers (electrons in this case) flow from the emitter toward the collector.

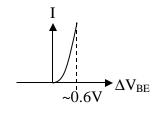

Also notice that in this configuration, the Emitter-Base form a reverse-biased diode. The I-V curve for that goes asymptotic at roughly 0.6V for silicon

Thus  $V_E = V_B - 0.6 \text{ V}$ .

## **Characterizing a Transistor / Convenient definitions**

With different electrical components, there are parameters that largely sum up their key behaviors in circuits; with a resistor, it's the resistance, R; with the capacitor, it's the capacitance, C. With the Transistor, there are three relevant relations.

$V_E = V_B - 0.6$  V as just argued.

$$\mathbf{a} \equiv \frac{I_C}{I_E}$$

, or, more commonly  $\mathbf{b} \equiv \frac{I_C}{I_B} = \frac{\mathbf{a}}{1 - \mathbf{a}} = h_{FE}$  is called the "current gain."

Often a transistor's "current gain" is a specified parameter.

And finally,  $I_c = I_E - I_B$  (as is obvious when you look at the flow diagram above).

Note that, since transistors are often manufactured (with very small base regions?) so as to make  $I_B \ll I_E$ , so **a** is quite close to 1.

## 8.2.2 External Circuit Configurations

Let's plug one of these things into a circuit and think about how it behaves. The book shows three common configurations and some different uses for them: the "Common" Emitter, Base, or Collector. Here, "common" means that the pin (emitter, base, or collector) is wired (more or less) directly to a voltage supply line – be that +, -, or ground.

We'll start with the Common Emitter configuration and consider it thoroughly before moving on to the other two.

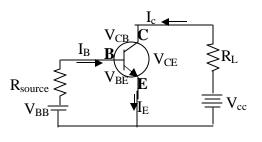

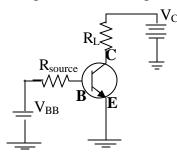

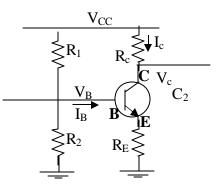

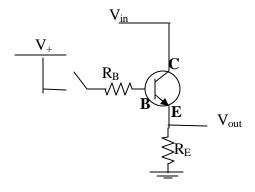

**Common Emitter** (emitter wired to common / ground)

The book shows it as

if it helps, we can unwrap it as

## 8.2.3 Characteristic Curves

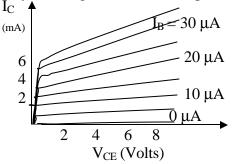

**Characteristic Curve.** A rather revealing characterization of the circuit is the family of "characteristic curves", that is, the current this passes through the load (collector current) as a function of the collector's voltage above ground ( $V_{CE}$ ) for different base currents (imagine the two batteries in the schematic being variable, so you change  $V_{BB}$ , then sweep through values of  $V_{CC}$  to generate one curve.)

Apparently, the first few tenths of a volt go to 'turning on' the reverse-biased diode formed by the Base and the Emitter. With that comes a tremendous gain in electrons that are free to travel the length of the transistor. Beyond that, most of the increased voltage further forward biases the Base-Collector diode which returns more modest, linear increases in current that can flow down the transistor.

If the source is wired to the Base and the load is wired to the Collector, then there is a significant current (and corresponding power) gain- micro-amp input currents lead to milli-amp output currents.

**Find Input Resistance.** Here's how one might analyze such a thing. Say  $V_{BB}$ ,  $V_{CC}$ ,  $R_s$  and  $R_L$  are known, and so is  $\beta$ . Then let's find the "input resistance" That is, what resistor would replace the transistor to have the same current from

the source, I<sub>B</sub>, and the same voltage drop to ground, V<sub>BE</sub>?  $R_{input} \equiv \frac{V_{BE}}{I_B}$

$R_{input} \equiv \frac{V_{BE}}{I_B}$   $V_{BE} \approx 0.6V \text{ (see bottom of page 4), } I_B = \frac{V_{BB}}{R_{source}}$ So,  $R_{input} \approx \frac{0.6V}{V_{BB}} R_{source}$

If, say,  $V_{BB} = 10$  V, and  $R_{source} = 500\Omega$ , then  $R_{input} = 30\Omega$ .

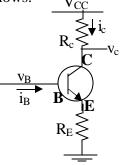

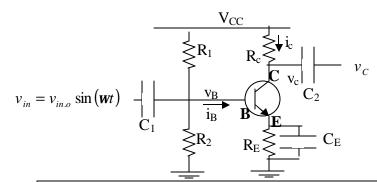

## 8.3 The Common-Emitter Amplifier

#### **Common Emitter Amplifier**

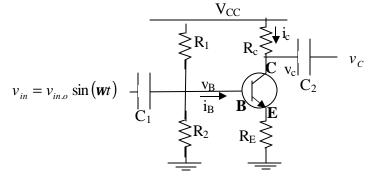

**Variation on a theme: Input & Output Resistance.** "Common" emitter doesn't always literally mean that the emitter is wired straight to ground, sometimes there's a resistor betweenit and ground. In that case, the input resistance can often be approximated as follows.  $V_{CO}$

**Note:** rather subtly, the voltages and currents are now in lower case, the book's notation for AC values, rather than DC values. This will impact how we can calculate some values.

$$\boldsymbol{b} \equiv \frac{i_C}{i_B}, \ R_{input} \equiv \frac{dv_B}{di_B}$$

while  $V_B \approx V_E + 0.6V$ , since the 0.6V is just a constant off-set,  $dv_B = dv_E$

Thus

$$R_{input} = \frac{dv_B}{di_B} = \frac{dv_E}{di_B}$$

But,  $v_E = R_E i_E$

So,

$$R_{input} \approx R_E \frac{di_E}{di_B}$$

where  $i_C = i_E - i_B \Rightarrow i_E = i_C + i_B$

$R_{input} \approx R_E \left(\frac{di_C}{di_B} + 1\right)$

And  $\boldsymbol{b} \equiv \frac{i_C}{i_B}$

So,  $R_{input} \approx R_E (\boldsymbol{b} + 1) \approx R_E \boldsymbol{b}$  since transistors are generally designed so that  $\boldsymbol{b} >> 1$ .

## 8.3.1 Input and Output Impedance

**Output Impedance.** For an alternating current signal, the output impedance is better defined as  $R_{out} \equiv \frac{dv_c}{di_c}$  than just the ratio of the two values. Now,

$V_{cc} - v_c = i_c R_c$  where  $V_{cc}$  is a constant, so,  $R_{out} \equiv \frac{dv_c}{di_c} = -R_c$  (the sign represents a phase flip in the signal)

flip in the signal).

**AC Gain.** This kind of circuit is usually used to amplify a signal, that is, if there's a small voltage applied at the base, a corresponding large voltage is generated at the collector. The ratio of the two would be the circuit's "voltage gain."

$$v_{B} = v_{B.o} \sin \left( \mathbf{w}t \right) \underbrace{\frac{V_{B}}{\mathbf{v}_{B}}}_{\mathbf{R}_{B}} \underbrace{\frac{V_{CC}}{\mathbf{R}_{c}}}_{\mathbf{R}_{c}} \underbrace{\frac{V_{CC}}{\mathbf{v}_{c}}}_{\mathbf{R}_{E}} \underbrace{\frac{V_{CC$$

How do the voltages at the Base and the Collector compare?

$$R_{input} \equiv \frac{dv_B}{di_B} \text{ where we've found that } R_{input} \approx R_E (\boldsymbol{b}+1) \approx R_E \boldsymbol{b}$$

$$\boldsymbol{b} \equiv \frac{i_C}{i_B} \text{ so } di_B = \frac{di_C}{\boldsymbol{b}}$$

then

$$R_E(\boldsymbol{b}+1) = \boldsymbol{b} \frac{dv_B}{di_c} \text{ or } R_E\left(1+\frac{1}{\boldsymbol{b}}\right) = \frac{dv_B}{di_c}$$

Meanwhile,

$$R_{out} \equiv \frac{dv_c}{di_c} = -R_c, \text{ so } di_c = -\frac{dv_c}{R_c}$$

Then

$$R_{E}\left(1+\frac{1}{\boldsymbol{b}}\right) = -R_{c}\frac{dv_{B}}{dv_{c}} \Longrightarrow \frac{dv_{c}}{dv_{B}} = -\frac{R_{c}}{R_{E}}\frac{1}{\left(1+\frac{1}{\boldsymbol{b}}\right)} \approx -\frac{R_{c}}{R_{E}}$$

So, there's our AC voltage gain,

$$\frac{dv_c}{dv_B} = -\frac{R_c}{R_E}$$

## **8.3.2** Biasing the Base

**Input Bias.** The astute reader might have noticed a problem with this gain. While this may be the voltage gain *while the transistor is functioning properly*, the transistor can't possibly produce an output voltage any lower then ground or higher than V<sub>CC</sub> the way it's wired up.

A related complication is that, as can be seen in the "characteristic curves,"  $\boldsymbol{b}$  is by no means a constant over the full range; for very small bias currents, the circuit 'turns on' rather dramatically before settling into nice linear behavior.

For both these reasons, it's nice to ensure that  $V_B$  is always high enough so that the transistor is "on", even while the input signal itself may oscillate around zero. Thus we modify the circuit just a little to offset the signal presented to the base. The first step in doing this is adding a voltage divider at the input.

We've just calculated the transistor's input impedance, i.e., what single resistor could replace the transistor and yield the same current drawn in the base for the same base voltage, that was

$$R_{input} \approx R_E \boldsymbol{b}$$

(not quite right for a *DC* signal, but, gets the right ballpark for an argument we'll make.) So, from the perspective of the base, the circuit looks like a voltage divider

Then

$$V_B = \frac{1}{1 + R_1 (1/R_2 + 1/R_{input})} V_{CC}$$

$$V_{CC}$$

$$R_1$$

$$V_B$$

$$R_2$$

$$R_2$$

$$R_1$$

$$R_2$$

$$R_2$$

$$R_1$$

$$R_2$$

Since the input impedance is quite large (thanks to b >>1), for reasonable R<sub>1</sub> and R<sub>2</sub>, we have

$$V_{B.bias} \approx \frac{1}{1 + R_1 (1/R_2)} V_{CC} \, . \label{eq:VB}$$

So,  $R_1$  and  $R_2$  would determine the base voltage in the absence of any other input signal. We'll call that  $V_{B \ bias}$ , and it's the base "bias" voltage.

Now, if we put a capacitor between this voltage divider and an input signal, the circuit looks like

The signal at the base is then

$$V_B = V_{B.bias} + v_{in}$$

$$V_B \approx \frac{1}{1 + R_1 (1/R_2)} V_{CC} + v_{in.o} \sin\left(\mathbf{w}t\right)$$

So it mimics the input signal, but rather than oscillating around zero, it oscillates around the bias voltage (you'll notice that a capacitor has also been added to the output so whatever additional bit of circuitry receives this circuit's output can play a similar game and set the voltage bias that it wants.) Recall that the transistor circuit can only produce outputs between  $V_{cc}$  and ground. So, we want to choose our input bias voltage (by choosing our R<sub>1</sub> and R<sub>2</sub>) so the corresponding output bias is right in the middle of this range – that would maximize the range of input signals for which the circuit behaved well.

So, we have

$$V_{B.bias} = \frac{1}{R_1 / R_2 + 1} V_{CC} \, .$$

And we want

$$V_{C.bias} = \frac{1}{2} V_{CC}$$

If we say the transistor has a DC voltage gain of G (that is,  $V_C / V_B = G$ ), then we want the base biased to

$$V_{B.bias} = V_{C.bias} / G$$

So, the resistors are chosen such that

$$\frac{1}{2}V_B / G = \frac{1}{R_1 / R_2 + 1}V_{CC}$$

$$2G = R_1 / R_2 + 1$$

#### **Thermal Stability**

A very high gain circuit operating on an AC signal oscillates between passing a lot of current, and not so much. While in the high-current fraction of its oscillation the transistor can get it hot. Raising its temperature means increasing the carrier population in the transistor, and thus decreasing its effective resistance and increasing the current still more. Effectively, the circuits gain oscillates – distorting the output signal. This is addressed by putting a capacitor in parallel with the emitter resistor.

$$v_{in} = v_{in,o} \sin(\mathbf{w}t) - \begin{bmatrix} V_{CC} & V_{C} \\ R_1 & R_c & I_c \\ V_B & C_1 & C_2 \\ R_2 & R_E & C_E \end{bmatrix}$$

This replaces  $R_E$  with  $\vec{Z}_E = \frac{R_E}{1 + j(R_E C_E 2\mathbf{p}f)} = \frac{R_E}{\sqrt{1 + (R_E C_E 2\mathbf{p}f)^2}} e^{-j \tan^{-1}(R_E C_E 2\mathbf{p}f)}$  as the reactance and the gain is then  $\frac{R_C}{\vec{Z}_E} = \frac{R_C}{R_E} \sqrt{1 + (R_E C_E 2\mathbf{p}f)^2} e^{j \tan^{-1}(R_E C_E 2\mathbf{p}f)}$

Clearly, the gain increases with frequency; so does the input impedance,  $bZ_E$ . Now, if we're only planning on running relatively high frequency signals through this, then we can still have a large gain but not necessarily draw as large a current – keeping things cooler and stable.

All told, the common emitter configuration is pretty handy.

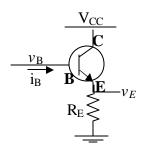

## 8.4 Common Collector-Emitter Follower

Now let's consider the Common Collector configuration. This can be used as a "follower."

11

Now the collector is wired directly to the positive power supply, and we're outputting the emitter voltage. At first blush, you might ask "what's the point?" Since  $V_E = V_B - 0.6V$ , there's no real *voltage* gain (just a slight DC offset, that doesn't matter for AC signals); however, there is a *current* gain.

Qualitatively, here's the beauty: the transistor acts as a buffer between two chunks of circuitry – (within reason) regardless of how much current is drawn out the emitter, it maintains the same voltage as dictated by the input at the base. So, for example, if you have a voltage divider wired up to the base, then the emitter maintains the desired voltage (dropped by 0.6V) regardless of what it's wired up to.

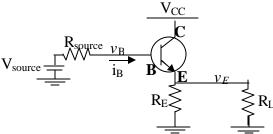

To quantitatively make this point, we'll imagine wiring this up to some source and some load.

**Input Impedance.**

$$R_{in} = -\frac{dv_B}{di_B} \text{ (sign because, current flows downhill)}$$

$$V_E = V_B - 0.6V \Rightarrow dv_E = dv_B$$

$$I_E = I_B (1 + \mathbf{b}) \Rightarrow di_B = di_E / (1 + \mathbf{b})$$

Note: current out the emitter splits and goes through the parallel resistors  $R_{\!E}$  and  $R_{\!L}.$

$$R_{in} = -\frac{dv_E}{di_E} (1 + \boldsymbol{b}) = \frac{R_E R_L}{R_E + R_L} (1 + \boldsymbol{b})$$

With b >>1, the input impedance can easily be mega-ohms. One implication is that very little current gets drawn out of the source and across the source's internal resistance; this means that there's very little voltage drop across the source's resistance and so  $V_{source} \approx V_B = V_E + 0.6V$ , regardless (mostly) of R<sub>L</sub>.

## **Output Impedance.**

$$R_{out} \equiv -\frac{dv_E}{di_E}$$

So, we need to build an expression for  $v_E$  in terms of  $i_E$  and make explicit how it depends upon the circuit elements.

$i_{E} = i_{E} - i_{E}'$  (the un-primed is the current flowing right out of the emitter, while the primed is that which continues on through R<sub>E</sub>, thus  $i_{E}' = \frac{v_{E}}{R_{E}}$ .)

As always,  $i_E = i_B + i_c = i_B (1 + \boldsymbol{b})$

Looking at the circuit, the base current is  $i_B = \frac{v_{source} - v_B}{R_{source}}$

As always,  $v_B = v_E + 0.6V$

Putting all this together,

$$i_{L} = \frac{v_{source} - v_{E} - 0.6V}{R_{source}} (1 + \mathbf{b}) - \frac{v_{E}}{R_{E}}$$

So,  $v_{E} = \frac{\frac{v_{source} - 0.6V}{R_{source}} (1 + \mathbf{b}) - i_{L}}{\frac{1}{R_{E}} + \frac{(1 + \mathbf{b})}{R_{source}}}$

So,  $R_{out} = -\frac{dv_{E}}{di_{E}} = \frac{1}{\frac{1}{R_{E}} + \frac{(1 + \mathbf{b})}{R_{source}}} = \frac{R_{E}R_{source}}{R_{source} + R_{E}(1 + \mathbf{b})} \approx \frac{R_{source}}{(1 + \mathbf{b})} \approx \frac{R_{source}}{(\mathbf{b})}$

If b >>1, then the output impedance can be quite tiny. That means that a very big current can be drawn for the output voltage.

There we have it, there's a very small current draw out of the source (large input impedance), but still a lot of current can be supplied at the output (small output impedance.)

**Current Gain.** With the "input" on the base and the "output" on the Emitter, one could roughly say that the current gain is

$\frac{l_E}{l_B} = \boldsymbol{b}$ . Of course, some of that current gets siphoned off, through RE rather than going through

the load. That current is a fraction of the total current coming out the emitter:

$$i_{Load} = i_E \frac{R_E}{R_E + R_L}$$

or  $i_{Load} = i_B \boldsymbol{b} \frac{R_E}{R_E + R_L}$

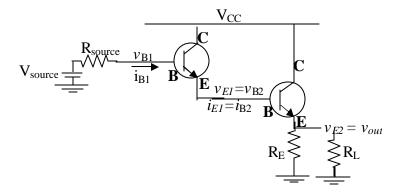

## 8.5 The Darlington Configuration

What if you want even *more* current gain? You daisy chain two common collector transistor in what's called the "Darlington" configuration.

#### **Current Gain**

$$i_{source} = i_{B1} = \frac{1}{b_1} i_{E1} = \frac{1}{b_1} i_{B2} = \frac{1}{b_1} \left( \frac{1}{b_2} i_{E2} \right) \Longrightarrow \frac{i_{E2}}{i_{B1}} = \boldsymbol{b}_1 \boldsymbol{b}_2$$

So the effective **b** of the combined transistors can be huge!

Strictly speaking, to relate the source current to the load current, we again have to factor in that only a fraction of the current exiting the emitter goes through the load (some goes through  $R_{E.}$ ) Thus

$$\frac{i_L}{i_{source}} = \boldsymbol{b}_1 \boldsymbol{b}_2 \frac{R_E}{R_E + R_L}$$

## **Input & Impedance**

The Darlington has a the same input impedance as does a single common collector transistor.

$$R_{in} = -\frac{dv_B}{di_B} \text{ (sign because, current flows downhill)}$$

$$V_{E2} = V_{B1} - 2 * 0.6V \Rightarrow dv_E = dv_B$$

$$I_{E2} = (I_{B1}(1 + \boldsymbol{b}_1))(1 + \boldsymbol{b}_2) \Rightarrow di_B = di_E / ((1 + \boldsymbol{b}_1)(1 + \boldsymbol{b}_2)) \approx di_E / (\boldsymbol{b}_1 \boldsymbol{b}_2)$$

$$R_{in} = -\frac{dv_E}{di_E} (\boldsymbol{b}_1 \boldsymbol{b}_2) = \frac{R_E R_L}{R_E + R_L} (\boldsymbol{b}_1 \boldsymbol{b}_2)$$

The output impedance can be found to be  $R_{out} \equiv -\frac{dv_E}{di_E} \approx \frac{R_{source}}{\boldsymbol{b}_1 \boldsymbol{b}_2}$  via a

similar derivation to that for the lone common collector transistor. (note: in the book's equations 8-23 and 8-24, the  $b^2$  should really be  $b_1b_2$ )

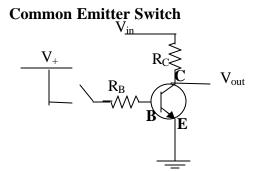

## 8.6 The Transistor Switch and Logic

The transistor is the basic unit of integrated circuits that, themselves, are the building blocks of all the electronic components that augment our modern lives. It is comparatively rare for a lone transistor be used; however, there is one rather common application: a transistor switch.

## **Common Collector Switch**

## Mechanical Switch Open -> Transistor Switch Open

$V_{out} = 0$  because negligible current flows through R<sub>E</sub>, so  $V_{out} - 0 = i_E R_E \approx 0 \Longrightarrow V_{out} \approx 0$

Mechanical Switch Closed -> Transistor Switch Closed

$$V_{out} - 0 = i_E R_E$$

$$i_E = i_B + i_c = (1 + \mathbf{b})i_B$$

$$i_B = (V_+ - V_{out} - 0.6V)/R_B$$

$$V_{out} = (1 + \mathbf{b})(V_+ - V_{out} - 0.6V)\frac{R_E}{R_B}$$

$$V_{out} = \frac{(1 + \mathbf{b})(V_+ - 0.6V)}{1 + (1 + \mathbf{b})\frac{R_E}{R_B}} \approx (V_+ - 0.6V)\frac{R_B}{R_E} \le V_+$$

Which, as long as  $R_B$  is a bit more than  $R_E$  means that  $V_{out}$  hits the ceiling at  $V_+$ . Notice that the exact value of  $V_{in}$  just doesn't mater (it just needs to be greater than VB for the transistor to operate propertly), so it's usually just wired to  $V_+$ .

15

#### Mechanical Switch Open -> Transistor Switch Closed

When the mechanical switch is open, there is no base current, so there is only a negligible collector and emitter current. That means that there's no voltage drop across  $R_c$ , and thus the output voltage is essentially the input voltage:

$$V_{out} - V_{in} = -i_c R_c \approx 0 \Longrightarrow V_{out} \approx V_{in}$$

It's important to point out that *this* switch can actually pass the specific value on  $V_{in}$ .

## Mechanical Switch Closed -> Transistor Switch Open

When the mechanical switch is closed, then there is a base current and there is a collector current,

$$V_{out} - V_{in} = -i_c R_c$$

$$i_c = \mathbf{b} i_B$$

$$i_B = \frac{V_+ - 0.6V}{R_B}$$

$$V_{out} = V_{in} - \mathbf{b} \frac{R_c}{R_B} (V_+ - 0.6V) \ge 0$$

Or, since the second term is apt to be larger than the first term, and the least  $V_{out}$  can really be is 0 (assuming  $V_{in}>0$ ),

$V_{out} = 0$

Note: if  $V_{in} < 0$ , then, in principle, the Collector is like an Emitter and the Emitter is like a Collector – it's like we flipped the transistor to have a common – collector switch (though I wouldn't expect it to behave too well since it wasn't designed for that.)

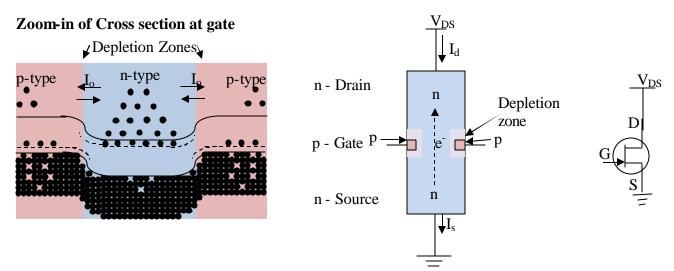

#### 8.7 Junction Field Effect Transistors

• **Transition.** We've spent a lot of time considering transistor circuits built around NPN Bipolar Junction transistors, and very similar circuits can be built of PNP transistors. There is a radically different kind of transistor that's worth knowing about, the Junction Field Effect Transistor, or the J-FET for short.

- **Qualitative Plumbing Analogy.** Qualitatively, to appreciate how the J-FET differs from the bipolar junction transistor, we'll imagine a plumbing analog.

- Bipolar Junction Transistor. Think of the regular Bipolar Junction transistor as a stretch of flexible piping it has a constant width and bends in it like in the figures on page 2 of the notes. The amount of flow down the length of the device depends on the voltage drops *down stream*, that from the collector to the base, and that from the base on to the emitter. The steeper these drops, the more current flows along the device.

- **Field Effect Transistor.** In contrast, a J-FET transistor is like a stretch of piping with a collar in the middle; that collar can be choked down or opened up to allow less or more flow. Sure, you still need an over-all voltage drop to drive current, but it's this widening and narrowing of the collar that plays the key role in controlling the flow.

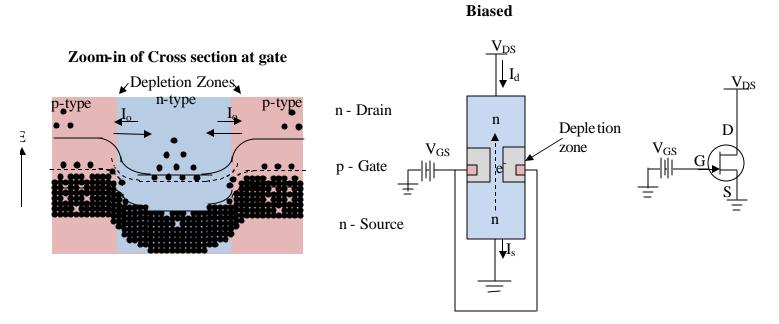

- **Depletion Zone at Junction.** The key to understanding how these J-FET's work is understanding what goes on at the junction. Here are a few different representations of the device.

Unbiased. First we'll look at it in the simple case, with the "gate" disconnected, and refresh our memory on the fundamental physics going on right at the junctions between N and P-type materials (stuff we first considered when we met Diodes last week.) Even when no additional voltage is applied to the P-type material, its energy levels shift relative to those in the N-type. This happens because, right at the junction, the extra electrons of the "donor" atoms in the N-type now have the option of migrating just a *little* over into the P-type and 'falling' down to join "acceptor" atoms. Thus they reduce their energies, and, in the process create a small charge separation (more electrons on the P-side of the junction than on the N-side) and so an electric field and so a voltage and energy difference. This process is self-limiting – the more electrons

E

migrate, the greater the electric field impeding subsequent electrons from doing the same, so eventually an equilibrium is established. That's what's responsible for the bending of the energy levels right at the junctions. This all should make sense and sound familiar from when we met the Diode. Now here's a part that, though true for any N-P junction, wasn't important enough to merit our attention before. Each electron that opts to leave a "donor" and join an "acceptor" is one less electron to get thermally promoted into the conduction band of the N-type (and one less hole to get thermally created in the valence band of the P-type). So, right around the junction, there is a "Depletion Zone" where there aren't so many mobile charge carriers (electrons in the conduction band and holes in the valence band.) With such a low carrier density, the Depletion Zone is a very poor conductor. Looking at the figure below, the wider the Depletion Zone is, the narrower the remaining channel through which current can flow down the transistor from the Drain to the Source.

• **Biased.** The width of the Depletion Zone (and, conversely, the narrowness of the channel) can be increased by biasing the Gate, as illustrated here.

Thus the current flowing from Drain to Source is controlled by the difference between the voltage applied to the gate and that in the channel, which would roughly be the average

of the drain voltage and the source voltage:  $V_G - \frac{V_D + V_S}{2}$ .

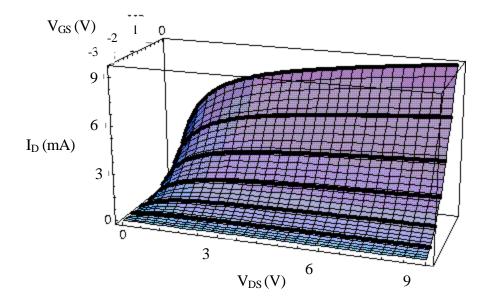

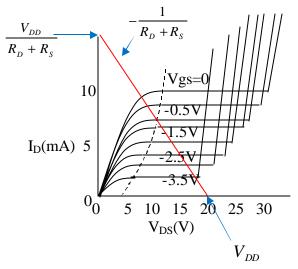

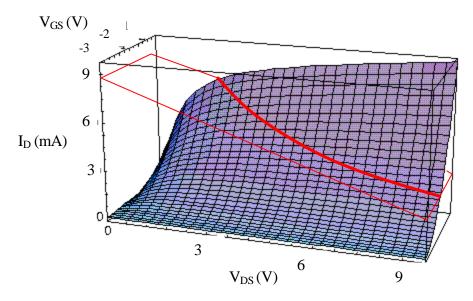

## Characteristic Curves and Pinch Voltage.

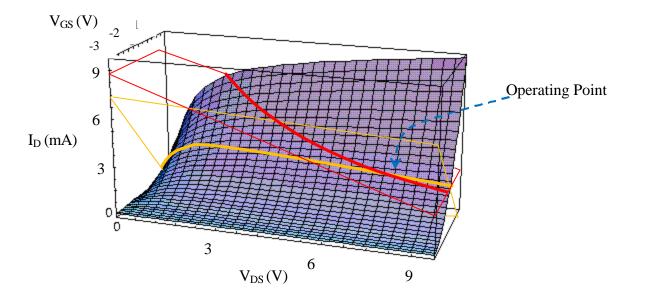

Three variables commonly characterize a JFET's behavior,  $V_{CS}$ ,  $V_{DS}$ , and  $I_D$ . Their relation to each other could be plotted in 3D as something like

Let's call this surface the "Operating Surface." As the JFET operates its is constrained so that its  $V_{GS}$ ,  $I_D$ , and  $V_{DS}$  values are on this surface. The dark lines trace curves of constant  $V_{GS}$ . These are called "Characteristic Curves."

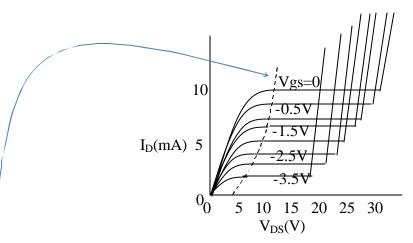

## I<sub>D</sub> vs V<sub>DS</sub> Characteristic Curves

First, looking straight down the V<sub>GS</sub> axis, and zooming out a little we see this.

You'll notice that, for low voltages, the current flowing down the transistor and out the Source goes linear with the voltage drop along its length,  $V_{DS}$ . However, for a given gate voltage,  $V_{GS}$ , there will come a drain voltage that corresponds to increasing the channel voltage so much that the depletion zones close in and *pinches-off* the channel. That value of  $V_{DS}$  is called the "pinch voltage",  $V_p$ . Naturally, the exact  $V_{DS}$  that does it depends upon the specific gate voltage,  $V_{GS}$ . A consideration of the geometry of the device, the density of donors & acceptors, and the voltage established in a depletion zone leads to a predicted curve for the pinch voltage as a function of the drain current – that's the dashed curve, characterized by

$$i_{D.pinch} = i_{DS-short} \left( 1 - \left( V_{GS} / V_{pinch} \right) \right)^2$$

(for a derivation, see section 6-4-1 of P.C. Dunn's Gateway into Electronics)

where  $i_{DS-short}$  is the current that passes in the Drain (and essentially that which passes on out the source) when the gate is short-circuited to the Source (say, both drain and source are grounded).

For higher voltages, the current remains fairly constant, until...something like a Zeener breakdown occurs between the gate and the drain, causing an avalanche of current, and the sudden jump on the right side of the plot.

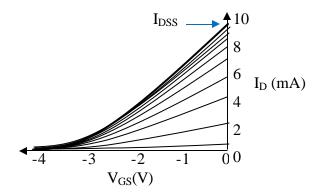

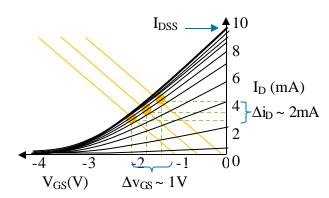

## I<sub>D</sub> vs V<sub>GS</sub> Transfer Curves

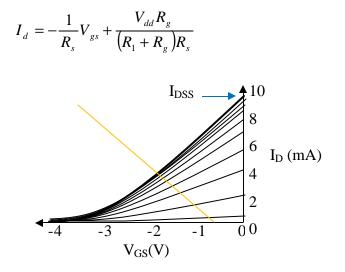

Look back at the 3-D rendering for a moment, see what the constant- $V_{DS}$  curves look like – roughly parabolic. Looking down the VDS axis would look something like this.

These graphical representations of the relationships between the three parameters, ID, VGS, and VDS, will help us visualize our analysis of a JFET in operation.

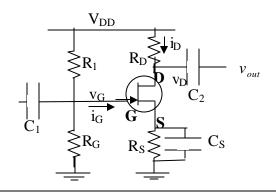

# **8.8** The FET Amplifier (for greater discussion, see Ch 6 of J.J. Brophy's <u>Basic Electronics</u> <u>for Scientists</u>.)

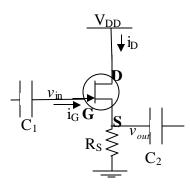

Well, now that we've familiarized ourselves with the basic character of a J-FET, let's see it in operation – the FET Amplifier in Common Source configuration. This is the J-FET's take on the Bipolar Junction's Common Emitter set-up that was discussed in section 8.3.

Common *Emitter* with input/output capacitors for AC signal (ignore offset), Base Bias, and Emitter capacitor for high-frequency stability

Common *Source* with same external circuit

Before we set our sites on any particular result, here are a few things worth knowing about a JFET in use.

In principle,  $I_D = I_s + I_G$  (since the channel carriers are electrons and the gate carriers are holes out of the device in this configuration, or equivalently electrons into it); however, a J-FET passes very little current between the Gate and the Source-Drain channel, (the sizable depletion zone acts as a barrier; read Section 8.10 about insulated gate transistors / MOSFET's to see this taken to the extreme), so

$$I_G \ll I_D, I_S$$

thus

$I_D \approx I_S$

More specifically,  $I_D$  is often in the mA range while  $I_G$  is in the nA range. So, even with a very large resistance between the Gate and ground,  $R_G$  on order of 0.1 to 10 M $\Omega$ , and an even larger resistor links it to the supply line,  $R_1$  around 20 to 100 M $\Omega$ .

$$V_G \ll V_D, V_S$$

Now, generally, when you wire up a transistor, the values of the resistors and the supply voltage ( $R_1$ ,  $R_G$ ,  $R_S$ , and  $V_{DD}$ ) are set, i.e., they're constants. Then the variables are  $I_D$ ,  $V_G$  (or  $V_{GS}$ ) and  $V_D$  (or  $V_{DS}$ ). If you supply an input voltage, then all three of these should be uniquely determined by that input voltage and the three constants ( $R_1$ ,  $R_G$ ,  $R_S$ , and  $V_{DD}$ .) We'll set about relating these variables to each other and the constants for the simplest case – when there is no input. So, we'll be finding the idle, or offset values of these current and voltages.

**Operating Point.** To visualize what we'll be doing, consider this. In  $I_D$ ,  $V_{GS}$ ,  $V_{DS}$  space, a JFET's operation 'lives' on the 3D surface illustrated on page 19. At a given moment (with given resistances, supply voltage, and input voltage), the set of values that the JFET has, ( $I_D$ ,  $V_{GS}$ ,  $V_{DS}$ ) define a point on that surface, that is referred to as the "operating point." Here's how we go about nailing down that Operating Point.

**Load-Line (in V\_{DS} - I\_D plane.)** Tracing the voltage drop down from  $V_{DD}$  to ground (for a DC current, or approximately for a low frequency current), we have

$$(V_{DD} - V_D) = I_D R_D$$

, but  $V_D = V_{DS} + I_S R_S$ , but if  $I_D \approx I_S$ ,

that's  $V_D = V_{DS} + I_D R_S$

So

$$(V_{DD} - V_{DS} - I_D R_S) = I_D R_D \Longrightarrow I_D = \frac{V_{DD} - V_{DS}}{R_D + R_S}$$

Re-arranging this a tad casts it as an equation of a line in the  $V_{ds}$ -I<sub>d</sub> plane, i.e., that in which we've sketched the Characteristic Curves. This is referred to as the "Load Line."

$$I_{D} = -\frac{1}{R_{D} + R_{S}} V_{DS} + \frac{V_{DD}}{R_{D} + R_{S}}$$

Looked at that way,  $R_D+R_S$  set the slope as well as the intercepts of that line.

In the 3D space of ID, VGS, VDS, we have defined a plane that slices through the Operating Surface. Where this plane intersects the surface defines a curve. As the JFET is constrained to both 'live' on this plane and on the Operating surface, it is constrained to live on the curve where they intersect. We're one step closer to nailing down the Operating Point.

Bias Line (in  $V_{GS}$  –  $I_D$  plane). Now for a little more math.

$$V_{gs} = V_g - V_s$$

Where  $V_s = I_s R_s$ , but  $I_s \approx I_d$  so  $V_s = I_d R_s$

As for  $V_g$ , assuming that negligible current runs in the gate, compared with that running through  $R_1$  and  $R_g$ , then the  $R_1$  and  $R_g$  approximately form a voltage divider giving the voltage at the gate as approximately

$$V_g \approx V_{dd} \, \frac{R_g}{R_1 + R_g}$$

Therefore, we have

$$V_{gs} = V_{dd} \frac{R_g}{R_1 + R_g} - I_d R_s.$$

Flipping this around to solve for Id, we have another equation of a line, this time in the  $V_{gs}$ -I<sub>d</sub> plane. It's known as the Bias Line.

In the  $V_{DS}$ ,  $V_{GS}$ ,  $I_D$  space, it defines a corresponding plane.

Again, this plane slices through the Operating Surface, and since the JFET's operation is confined to both, it is confined to the curve of their intersection. But since it's also confined to the curve of the intersection of the Load Plane and the Operating Surface, it is completely confined to the point where these two curves intersect – the Operating Point! Thus, Voltages and current are uniquely determined. All this was argues assuming that we had no input signal, so we've got a qualitative sense for how the idle, or offset values of  $V_{DS}$ ,  $V_{GS}$ , and  $I_D$  are set. Clearly, there would be a considerable, though steady, output signal even when there is no input signal.

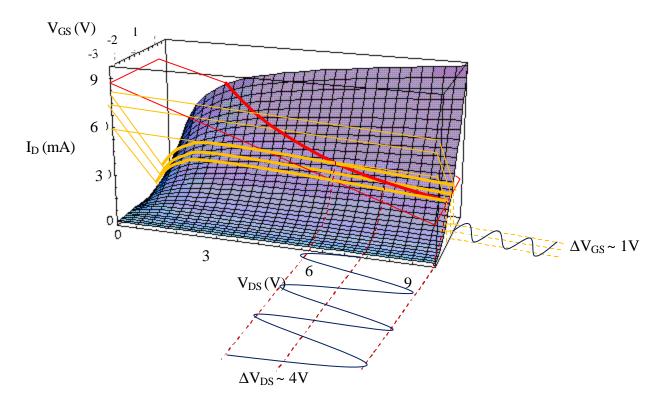

## **Include Input Signal**

Now, if all you're interested in doing is amplifying an AC signal, you don't care about these offsets. So you put capacitors on the output and input lines. Qualitatively, we can reason how the circuit would process an AC input signal.

Adding an oscilating input signal would wiggle the gate voltage just as if we were varying R1. Looking at the equation of our Bias Line, the effect *that* would have is wiggling the line's offset (while maintaining its slope). In the 3D plot on page 23, that essentially slides the yellow curve up and down the Operating surface, thus changing the point of its intersection with the red line – the operating point.

As illustrated below, an oscillating V<sub>GS</sub> leads to a larger, *amplified*, oscillating V<sub>DS</sub>.

From this particular angle, it's a little harder to see, but changing VGS means also changing  $I_D$ . Let's say that, viewed in the  $V_{GS}$ - $I_D$  plane, the three operating points illustrated here are

The ratio of the *output* variation in current to the *input* variation in voltage is the "Transconductance",

$$g_m \equiv \frac{\Delta i_D}{\Delta v_{gs}}$$

Looking back at the circuit, we can recall that  $\frac{V_{DD} - V_D}{R_D} = I_D$  so a variation in the current of  $\Delta i_D$  results in a variation of the drain voltage of  $\Delta v_D = -\Delta i_D R_D$ .

Then the ratio of variations in the *output voltage* to variations in the *input voltage*, i.e., the voltage gain, is

$$A_{v} = \frac{\Delta v_{D}}{\Delta v_{GS}} = R_{D} g_{m}$$

#### 8.9 FET Follower

Now that we've tackled the FET in a slightly complicated circuit, we'll back off and look at one that's as simple as can be.

Let's see how the input and output are related.

$$V_{in} - V_{out} = V_{GS}$$

Now, if we're just concerned with AC signals (as I've suggested by wiring this up through capacitors), then we can recast this as

$$\Delta v_{in} - \Delta v_{out} = \Delta v_{GS}$$

where  $g_m \equiv \frac{\Delta i_D}{\Delta v_{gs}}$  or  $\Delta v_{gs} = \frac{\Delta i_D}{g_m}$

but  $V_{out} = I_D R_S$  so  $\Delta i_D = \frac{\Delta v_{out}}{R_S}$

Putting these together gives

$$\Delta v_{in} - \Delta v_{out} = \frac{\Delta v_{out}}{g_m R_s}$$

or

$$\Delta v_{out} = \frac{\Delta v_{in}}{1 + \frac{1}{g_m R_s}}$$

That's a fairly general result, but, if we have a fairly large  $R_S$ , such that

$\frac{1}{g_m R_s} \ll 1$  (and that's quite often the case), then

$\Delta v_{out} \approx \Delta v_{in}$

You may ask, 'so what's the point of using a FET like this?' The answer lies in the fact that the FET draws exceedingly little current in its Gate. So this circuit has a very high input impedance. It makes a great follower.